AS4C32M16D2C-25BCN

Siehe Produktspezifikationen

Herst.:

Beschreibung:

DRAM DDR2, 512Mb, 32M x 16, 1.8V, 84-ball BGA, 400 MHz, Commercial Temp - Tray

Auf Lager: 198

-

Lagerbestand:

-

198 sofort lieferbarEin unerwarteter Fehler ist aufgetreten. Bitte versuchen Sie es später noch einmal.

-

Lieferzeit ab Hersteller:

-

6 Wochen Geschätzte Produktionszeit des Werks für Mengen, die größer als angezeigt sind.

Preis (CHF)

| Menge | Stückpreis |

Erw. Preis

|

|---|---|---|

| CHF 3.66 | CHF 3.66 | |

| CHF 3.38 | CHF 33.80 | |

| CHF 3.28 | CHF 82.00 | |

| CHF 3.21 | CHF 160.50 | |

| CHF 3.13 | CHF 313.00 | |

| CHF 3.03 | CHF 633.27 | |

| CHF 2.96 | CHF 1'237.28 | |

| CHF 2.93 | CHF 3'061.85 | |

| CHF 2.80 | CHF 7'022.40 |

Datenblatt

- CAHTS:

- 8542320020

- USHTS:

- 8542320032

- MXHTS:

- 8542320299

- ECCN:

- EAR99

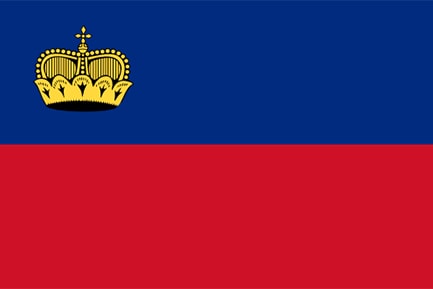

Liechtenstein

Liechtenstein