LS1022ASN7EKB

Siehe Produktspezifikationen

Herst.:

Beschreibung:

Mikroprozessoren - MPU Layerscape 32-bit Arm Cortex-A7, Dual-core, 600MHz, 0 to 105C, Security disabled

Verfügbarkeit

-

Lagerbestand:

-

Nicht auf LagerEin unerwarteter Fehler ist aufgetreten. Bitte versuchen Sie es später noch einmal.

-

Lieferzeit ab Hersteller:

-

39 Wochen Geschätzte Produktionszeit des Werks.

Preis (CHF)

| Menge | Stückpreis |

Erw. Preis

|

|---|---|---|

| CHF 27.49 | CHF 2’309.16 |

Datenblatt

- CNHTS:

- 8542319091

- CAHTS:

- 8542310000

- USHTS:

- 8542310045

- KRHTS:

- 8542311000

- TARIC:

- 8542319000

- MXHTS:

- 8542310302

- ECCN:

- 3A991.a.1

- Ursprungsland:

- Taiwan

- Herstellungsland:

- Taiwan

- Land der Verbreitung:

- Taiwan

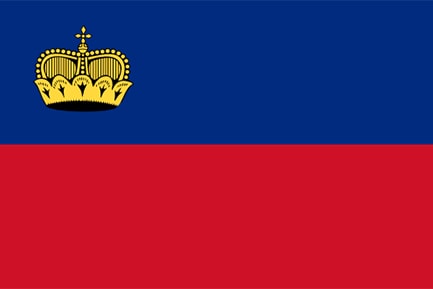

Liechtenstein

Liechtenstein