Infineon Technologies PSoC4100S ARM® Cortex®-M0 Programmierbare SoCs

Die ARM® Cortex®-M0 programmierbaren SoCs PSoC4100S von Cypress Semiconductor sind eine skalierbare und rekonfigurierbare Plattform-Architektur von programmierbaren eingebetteten System-Kontrollern. Die PSoC4100S kombinieren analoge und digitale Blöcke mit flexiblem automatischen Routing. Der PSoC4100S kombiniert einen Mikrocontroller mit standardmäßigen Kommunikations- und Timing-Peripheriegeräten. Ebenfalls kombiniert sind ein kapazitives Touch-Sensing-System (CapSense), programmierbare, universell einsetzbare zeitkontinuierliche und geschaltete Kondensator-Analogblöcke sowie programmierbare Konnektivität. Die PSoC 4200L-Produkte sind aufwärtskompatibel mit den Produkten der PSoC 4-Plattform für neue Applikationen und Design-Anforderungen.Merkmale

- 32-bit MCU Subsystem

- 48MHz Arm Cortex-M0+ CPU

- Up to 64KB of flash with read accelerator

- Up to 8KB of SRAM

- Programmable analog

- Two opamps with reconfigurable high-drive external and high-bandwidth internal drive, comparator modes, and ADC input buffering capability

12-bit 1Msps SAR ADC with differential and single-ended modes, and channel Sequencer with signal averaging - Single-slope 10-bit ADC function provided by a capacitance sensing block

- Two current DACs (IDACs) for general-purpose or capacitive sensing applications on any pin

- Two low-power comparators that operate in Deep Sleep low-power mode

- Two opamps with reconfigurable high-drive external and high-bandwidth internal drive, comparator modes, and ADC input buffering capability

- Programmable digital

- Programmable logic blocks allow Boolean operations to be performed on port inputs and outputs

- Low-power 1.71V to 5.5V operation

- Deep sleep mode with operational analog and 2.5µA digital system current

- Capacitive sensing

- Cypress CapSense Sigma-Delta (CSD) provides best-in-class signal-to-noise ratio (SNR) (>5:1) and water tolerance

- Cypress-supplied software component makes capacitive sensing design easy

- Automatic hardware tuning (SmartSense™)

- LCD Drive capability

- LCD segment drive capability on GPIOs

- Serial communication

- Three independent run-time reconfigurable Serial Communication Blocks (SCBs) with reconfigurable I2C, SPI, or UART functionality

- Timing and pulse-width modulation

- Five 16-bit timer/counter/pulse-width modulator (TCPWM) blocks

- Center-aligned, Edge, and Pseudo-random modes

- Comparator-based triggering of Kill signals for motor drive and other high-reliability digital logic applications

- Up to 36 programmable GPIO pins

- 48-pin TQFP, 44-TQFP, 40-pin QFN, 32-pin QFN, and 35-ball WLCSP packages

- Any GPIO pin can be CapSense, analog, or digital

- Drive modes, strengths, and slew rates are programmable

- PSOC Creator Design Environment

- Integrated Development Environment (IDE) provides schematic design entry and build (with analog and digital automatic routing)

- Application Programming Interface (API) component for all fixed-function and programmable peripherals

- Industry-standard tool Compatibility

- After schematic entry, development can be done with Arm-based industry-standard development tools

Videos

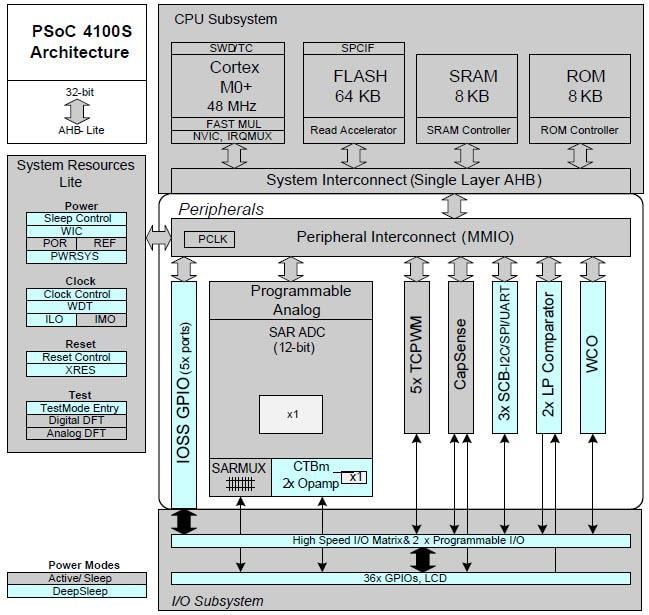

Block Diagram

Veröffentlichungsdatum: 2017-01-17

| Aktualisiert: 2025-08-19